The Importance of Energy Efficiency in Engineering and Informatics

Jeffrey Ludwig*

Department of Mathematics, University of California, USA

*Corresponding author: Jeffrey Ludwig, Department of Mathematics, University of California, Irvine, Rowland Hall 540H, Irvine, CA 92697, USA

Article History

Received: May 18, 2021 Accepted: May 20, 2021 Published: May 24, 2021

Citation: Ludwig J. The Importance of Energy Efficiency in Engineering and Informatics. Int J Eng Tech & Inf. 2021;2(2):48‒50. DOI: 10.51626/ijeti.2021.02.00012

Abstract

Techniques for reducing power consumption in digital circuits that underly automatic control of modern engineering systems are of paramount importance due to the simultaneously growing demands for portable multimedia devices and energy conservation. Digital filters, being ubiquitous in such devices, are thus a prime candidate for low power design. We review an algorithmic approach to low power frequency-selective digital filtering, an essential ingredient for energy efficient technological innovation in many domains.

Keywords: Low-power digital filters; Adaptive signal processing; Approximate signal processing

Background

Energy efficiency is of paramount importance for a broad class of engineering applications designed to operate in environments with limited resources. Energy consumption in mobile wireless communications systems, for example, is typically proportional to computational complexity. A well-established method for reducing computational complexity in wireless communications systems has been to precompute approximations to the communications signals before transmitting them via the telecommunications network. Reducing, or compressing, the number of bytes required for signal representation and modulation directly attenuates the required amount of computation for fast, robust, and reliable transmission and reception. The amount of compression may be dialed in to ensure the signal quality is sufficient for the particular application, introducing an available range of computational cost and quality operating points that the systems engineer may choose from. Innovations in source coding methodologies in speech, image, and video signal processing seek to eradicate unnecessary redundancy and derive flexible signal representations in their purest, most compendious form. Vector quantization and wavelets are two exemplary and successful methods used in image and video source coding [1]. A natural extension to variable source coding in signal processing is approximate processing, in which the algorithms for computation are intelligently abbreviated to conserve power instead of the signals themselves [2,3]. This again introduces an available range of computational cost and quality operating points that the systems engineer may choose from with the goal of achieving the desired level of system performance while simultaneously maximizing energy efficiency.

The demand for energy efficiency has grown immensely over the past decade. Low-power speech recognition is now popular in mobile devices [4,5]. Energy efficient engineering is now used in wearable devices [6], ingestible electronics [7,8], and cryptographic engines [9].

In this paper we review the problem of dynamically reducing computational cost while maintaining a desired level of output quality in frequency-selective digital filtering [10]. More specifically, we consider minimizing the average power consumption of a frequency-selective digital filter, subject to the constraint that a desired signal to noise ratio (SNR) at the output is maintained.

Results

In this section the results of computer simulation experiments involving speech signals are reviewed to demonstrate the practical viability of approximate filtering for low-power, energy efficient signal processing. We observe that a significant reduction in power consumption over fixed-order filters is possible using approximate filtering algorithms.

We present a computer simulation which shows that significant power savings may be achieved when the order of a digital filter is dynamically varied to provide time-varying stopband attenuation in proportion to the time-varying SNR of the input signal, while maintaining a fixed level of output quality. The experiment involves speech signals to demonstrate the practical viability of the low-power adaptive digital filter.

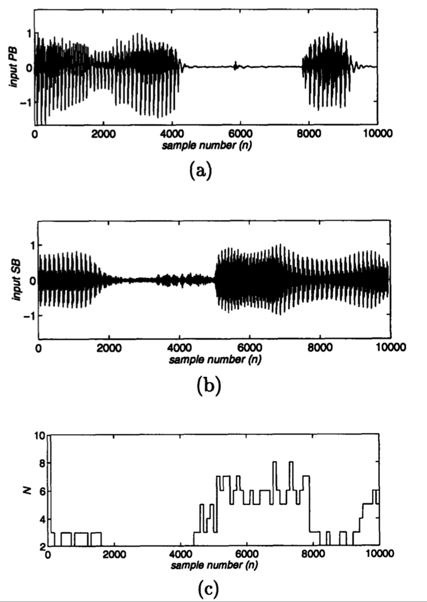

An approximate filter structure with 10 second-order sections is applied to two frequency-division multiplexed speech signals. We show in Figure 1 the input signal components in the passband, the input signal components in the stopband, and the dynamic adaptation of the filter order. Examination of the figure shows that, as would be expected, when the input SNR is low, then the filter order is large. We can also see that when the input SNR is high, then the filter order small. If we compare the power consumption for the low-power adaptive filter to the power consumption of a fixed-order filter needed to handle the worst-case signal statistics, we see that a power reduction of approximately 63% is achieved in this simulation. This approximation is based on visual inspection of Figure 1, where we can see two things: 1) the adaptive filter order over time ranges between 2 and 10, and 2) the order of a fixed-order filter that would ensure we are able to maintain the same minimum tolerable output SNR at all times is 8. It is important to note that the dynamic adaptation of the digital filter order depends on input signal statistics, so the power savings achieved will also depend on the input signal statistics. The basic idea is very simple and offers great potential for saving power and thus elongating mobile phone usage time before batteries are drained: dynamically minimize power consumption while maintaining the minimum required algorithmic performance.

Figure 1: Demultiplexing of FDM speech using low power frequency selective filtering. (a) passband speech, (b) stopband speech, and (c) number of filter sections as a function of sample number.

Discussion

The low-power digital filter using adaptive approximate processing reviewed in this paper is a part of a surge in research in energy efficient systems engineering. Another part of this movement is digital filtering using data-driven clock gating and multibit flip-flops combined, which has achieved 22% to 25% power reduction compared to that using a conventional design [11]. In another study, an energy efficient digital filter achieved nearly 70% reduction in energy with a negligible deviation of the frequency response from the standard implementation [12]. As a third example, in simulations using speech signals, a low power reconfigurable FIR digital filter based on dual mode operation achieved power savings up to 37.97% [13]. These results demonstrate how low-power digital signal processing continues to be a stimulating area of focused interest and innovation.

Conclusion

The signal processing demands of portable multimedia devices will continue to soar as mobile communications devices continue to shrink in size and require increasing computational speed and complexity. These increased demands are accompanied by definite constraints on power consumption since mobility is a now a firm consumer expectation, not just a desirable feature. The important task of designing low power, computationally powerful processors has emerged and spurred great interest and activity in signal processing research. In this paper we have reviewed a formulation for an algorithmic approach to low power frequency-selective digital filtering. We have seen that significant power savings may be achieved in digital filtering applications when the order of a digital filter is dynamically varied to provide time-varying stopband attenuation in proportion to the time-varying SNR of the input signal, while maintaining a fixed SNR at the filter output. This is just one example of the many exciting developments in energy efficient innovations that will provide a base for future researchers to build upon.

References

- Jayant NS, Noll P (1984) Digital coding of waveforms: principles and applications to speech and video.Prentice Hall: Englewood Cliffs; NJ: pp. 688.

- Nawab SH, Oppenheim AV, Chandrakasan AP, Ludwig JT, Winograd JM (1997) Approximate signal processing. Journal on VLSI Signal Processing15: 177-200.

- Winograd JM, Cummington ST, Hamid Nawab S, Clement Karl W (1997) Incremental Refinement Structures for Approximate Signal Processing. Boston University, USA.

- Price M, Glass J, Chandrakasan AP (2018). A Low-Power Speech Recognizer and Voice Activity Detector Using Deep Neural Networks. IEEE Journal of Solid-State Circuits 53(1): 66-75.

- Calhoun BH, Daly DC, Verma N, Finchelstein D, Wentzloff DD, et al. (2005) Design Considerations for Ultra-low Energy Wireless Microsensor Nodes. IEEE Transactions on Computers 54(6): 727-749.

- Tikekar M, Sze V, Chandrakasan AP (2018) A fully integrated energy-efficient H.265/HEVC decoder with eDRAM for wearable devices. IEEE Journal of Solid-State Circuits 53(8): 2368-2377.

- Steiger C, Abramson A, Nadeau P, Chandrakasan AP, Langer R, et al. (2018) Ingestible electronics for diagnostics and therapy. Nature Reviews Materials 4(2): 83-98.

- Mimee M, Nadeau P, Hayward A, Carim S, Flanagan S, et al. (2018) An ingestible bacterial-electronic system to monitor gastrointestinal health. Science 360(6391): 915-918.

- Banerjee U, Wright A, Juvekar C, Waller M, Arvind et al (2019). An energy-efficient reconfigurable DTLS cryptographic engine for securing internet-of-things applications. IEEE Journal of Solid-State Circuits 54(8): 2339-2352.

- Ludwig JT, Nawab SH, Chandrakasan AP (1996) Low-power digital filtering using approximate processing. IEEE J Solid State Circuits 31(3): 395–400.

- Agathoklis P, Touil L, Hamdi A, Gassoumi I, Mtibaa A (2020) Design of low-power structural FIR filter using data-driven clock gating and multibit flip-flops. Journal of Electrical and Computer Engineering.

- Pilipovic R, Risojevic V, Bulic P (2021) On the design of an energy efficient digital IIR A-weighting filter using approximate multiplication. Sensors (Basel) 21(3): 732.

- Padmapriya S, Lakshmi Prabha V (2015) Design of an efficient dual mode reconfigurable FIR filter architecture in speech signal processing. Microprocessors and Microsystems 39(7): 521-528.